# **SOFA Documentation**

Release 1.0

Xifan Tang

# **DEVICE FAMILY**

| 1  | Introduction                                                                                                                              | 1                                |

|----|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2  | HD FPGAs  2.1 Device Comparison  2.2 DC and AC Characteristics  2.3 Chip Gallery                                                          | 3<br>3<br>4                      |

| 3  | SOFA HD  3.1 Architecture  3.2 I/O Resources  3.3 Configurable Logic Block  3.4 Circuit Designs  3.5 Timing Annotation                    | 9<br>12<br>14<br>16<br>18        |

| 4  | QLSOFA HD  4.1 Architecture  4.2 I/O Resources  4.3 Configurable Logic Block  4.4 Circuit Designs  4.5 Timing Annotation                  | 21<br>23<br>25<br>28<br>28       |

| 5  | SOFA CHD  5.1 Architecture  5.2 I/O Resources  5.3 Configurable Logic Block  5.4 Circuit Designs  5.5 Timing Annotation  5.6 Custom Cells | 31<br>31<br>31<br>31<br>32<br>34 |

| 6  | Contacts                                                                                                                                  | 41                               |

| 7  | Acknowledgment                                                                                                                            | 43                               |

| 8  | Indices and tables                                                                                                                        | 45                               |

| In | dex                                                                                                                                       | 47                               |

**CHAPTER**

**ONE**

## INTRODUCTION

*Skywater Opensource FpgA* (SOFA) is a fully open-source embedded FPGA IP library, from the architecture description to production ready layouts. As illustrated in Fig. 1.1, SOFA IPs are designed through the Skywater 130nm PDK, OpenFPGA framework and Synopsys IC Compiler II. The runtime of the design flow for each IP is within 24 hours.

All the SOFA FPGAs are designed to interface the Caravel SoC interface. We aims to empower embedded applications with its low-cost design approach but high-density architecture.

Fig. 1.1: 24-hour FPGA IP development: from PDK to production-ready layout

### **HD FPGAS**

# 2.1 Device Comparison

The High Density (HD) FPGAs are embedded FPGAs built with the Skywater 130nm High Density Standard Cell library (Sky130\_fd\_SC\_HD).

Resource/Capacity SOFA HD QLSOFA HD SOFA CHD Look-Up Tables<sup>1</sup> 1152 1152 1152 Flip-flops 2304 2304 2304 Soft Adders<sup>2</sup> N/A 1152 1152 Routing Channel Width<sup>3</sup> 40 60 60 50MHz Max. Configuration Speed<sup>4</sup> 50MHz 50MHz Max. Operating Speed<sup>4</sup> 50MHz 50 MHz 50MHz User I/O Pins<sup>5</sup> 144 144 144 Max. I/O Speed<sup>4</sup> 33MHz 33MHz 33MHz Core Voltage 1.8V 1.8V 1.8V

Table 2.1: Logic capacity of High Density (HD) FPGA IPs

### 2.2 DC and AC Characteristics

### 2.2.1 Recommended Operating Conditions

Symbol Description Min Typical Max Units VDD\_io Supply voltage for I/Os 1.8 3.3 5.0 V VDD core Supply voltage for FPGA core V 1.62 1.8 1.98 Input voltage for other I/Os 3.3 V V\_in TBD TBD I\_in Maximum current through pins N/A TBD TBD mA TBD Maximum frequency of I/Os N/A TBD MHz f\_max

Table 2.2: Recommended Operating Conditions

<sup>1</sup> counted by 4-input fracturable Look-Up Tables (LUTs), each of which can operate as dual-output 3-input LUTs or single-output 4-input LUT.

<sup>&</sup>lt;sup>2</sup> counted by 3-input Look-Up Tables (LUTs) that are organized as a carry chain

<sup>&</sup>lt;sup>3</sup> counted by number of uni-directional routing tracks per tile

<sup>&</sup>lt;sup>4</sup> bounded by the maximum speed of GPIO cells of Skywater 130nm PDK. Higher speed may be expected when a high-speed GPIO cell is available.

$<sup>^{\</sup>rm 5}$  I/Os are divided into two groups: GPIOs and embedded I/Os.

**Note:** Threshold voltage of logic I for I/O (V\_OH) is  $0.8 * \text{VDD\_io}$ . In other words, V\_in should be at least 2.64V in order to be sensed as logic I

**Note:** Threshold voltage of logic  $\theta$  for I/O (V\_OH) is 0.4. In other words, V\_in should not exceed 0.4V in order to be sensed as logic  $\theta$ .

## 2.2.2 Typical AC Characteristics

Table 2.3: Typical AC characteristics for FPGA I/Os

| Symbol          | Description                               | Min | Max | Units |

|-----------------|-------------------------------------------|-----|-----|-------|

| V_in Overshoot  | Maximum allowed overshoot voltage for Vin | TBD | TBD | V     |

| V_in Undershoot | Minimum allowed overshoot voltage for Vin | TBD | TBD | V     |

| I_VDD_core      | Quiescent VDD_core supply current         | TBD | TBD | mA    |

| I_VDD_io        | Quiescent VDD_io supply current           | TBD | TBD | mA    |

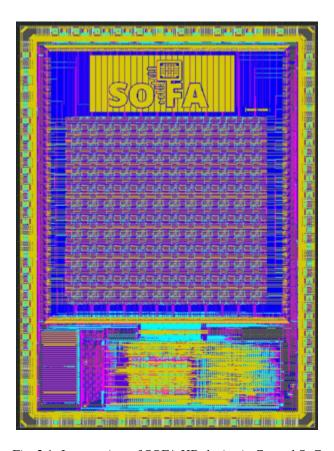

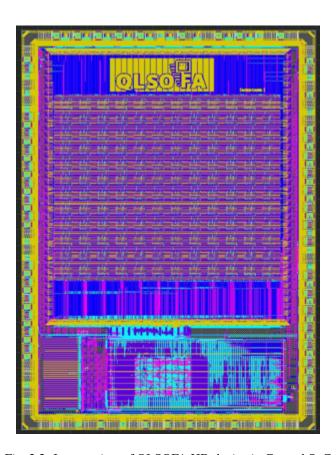

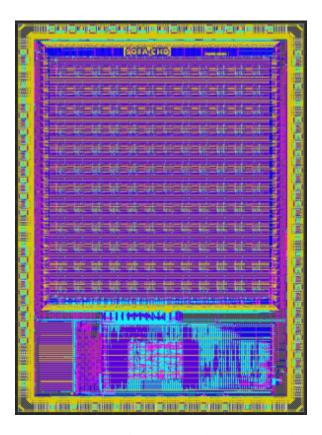

# 2.3 Chip Gallery

Here lists the images of each HD FPGA chips

### 2.3.1 SOFA HD

SOFA HD is the base design of the SOFA high-density eFPGA IPs

### 2.3.2 QLSOFA HD

QLSOFA HD is the arithmetic-enhanced design of the SOFA high-density eFPGA IPs

### **2.3.3 SOFA CHD**

SOFA CHD is the performance-optimized design of the SOFA high-density eFPGA IPs

Fig. 2.1: Layout view of SOFA HD device in Caravel SoC

2.3. Chip Gallery 5

Fig. 2.2: Layout view of QLSOFA HD device in Caravel SoC

Fig. 2.3: Layout view of SOFA CHD device in Caravel SoC

2.3. Chip Gallery 7

**CHAPTER**

**THREE**

## **SOFA HD**

### 3.1 Architecture

## 3.1.1 Floorplan

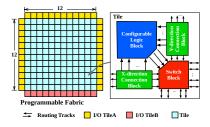

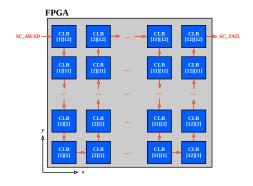

Fig. 3.1 shows an overview on the architecture of the embedded FPGA fabric. The FPGA follows a homogeneous architecture which only contains single type of tiles in the center fabric. I/O tiles are placed at the boundary of the FPGA to interface with GPIOs and RISC-V processors (see details in I/O Resources).

Fig. 3.1: Tile-based FPGA architecture

### 3.1.2 Tiles

The FPGA architecture follows a tile-based organization, to exploit the fine-grainularity in physical design, where three types of tiles are built:

Table 3.1: FPGA tile type and functionalities

| Туре | Capacity | Description                                                                                                                                                                                                                                           |

|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLB  | 144      | Each CLB tile consists of  - a Configurable Logic Block (CLB)  - a X-direction Connection Block (CBx)  - a Y-direction Connection Block (CBy)  - a Switch Block (SB).  This is the majority tile across the fabric to implement logics and registers. |

| IO-A | 36       | The type-A I/O is a low-density I/O tile which is designed to mainly interface the GPIOs of the SoC.  Each I/O-A tile consists of 1 digitial I/O cell.                                                                                                |

| ІО-В | 12       | The type-B I/O is a high-density I/O tile which is designed to mainly interface the wishbone interface and logic analyzer of the SoC.  Each I/O-B tile consists of 9 digitial I/O cells.                                                              |

### 3.1.3 Routing Architecture

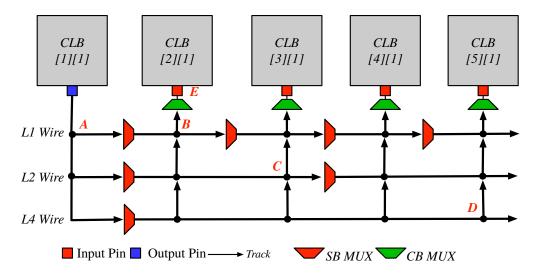

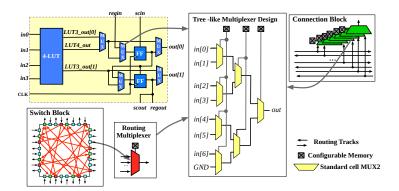

The routing architecture is based on uni-directional routing tracks, which are interconnected by routing multiplexers. Fig. 3.2 illustrates the detailed organization of the routing architecture.

The routing architecture consists the following type of routing tracks:

- Length-1 wires (L1 wires), which hop over 1 logic block (including I/O block)

- Length-2 wires (L2 wires), which hop over 2 logic block (including I/O block)

- Length-4 wires (L4 wires), which hop over 4 logic block (including I/O block)

Each tile includes two routing channels, i.e., the X-direction routing channel and the Y-direction routing channel, providing horizental and vertical connections to adjacent tiles. Each routing channel consists of 40 routing tracks. See details in Table 3.2.

Fig. 3.2: Detailed routing architecture

Table 3.2: Routing track distribution of SOFA HD FPGA

| Track type | Number of tracks per channel |

|------------|------------------------------|

| Length-1   | 4 (10%)                      |

| Length-2   | 4 (10%)                      |

| Length-4   | 32 (80%)                     |

| Total      | 40                           |

### 3.1.4 Scan-chain

There is a built-in scan-chain in the FPGA which connects the the  $sc_in$  and  $sc_out$  ports of CLBs in a chain (see details in  $Scan\ Chain$ ), as illustrated in Fig. 3.3.

When Test\_en signal is active, users can

- overwrite the contents of all the D-type flip-flops in the FPGA by feeding signals to the SC\_HEAD port

- readback the contents of all the D-type flip-flops in the FPGA through the SC\_TAIL port.

Fig. 3.3: Built-in scan-chain across FPGA

3.1. Architecture

### 3.2 I/O Resources

### 3.2.1 Pin Assignment

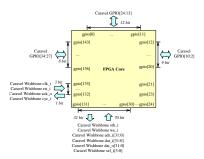

The High-Density (HD) FPGA IP has 144 data I/O pins as shown in Fig. 3.4.

Among the 144 I/Os,

- 29 external I/Os are accessible through the Caravel SoC's General-Purpose I/Os (GPIOs).

- 115 internal I/Os are accessible through the Caravel SOC's logic analyzer and wishbone interfaces, which are controlled by the RISC-V processor. See *Debug Mode* and *Accelerator Mode* for details.

**Warning:** For all the unused GPIOs, please set them to **input** mode, so that the FPGA will not output any noise signals to damage other SoC components.

**Note:** The connectivity of the 115 internal I/Os can be switched through a GPIO of Caravel SoC. As a result, the FPGA can operate in different modes.

**Warning:** The internal I/O pins will drive either Wishbone or the logic analyzer, following the same truth table as mode-switch bit in Fig. 3.4.

Fig. 3.4: I/O arrangement of *High-Density* (HD) FPGA IP: switchable between logic analyzer and wishbone bus interface

### 3.2.2 External I/Os

A SOFA HD FPGA IP contains 37 external I/O pins, including 29 data I/Os and 8 control I/Os.

Full details are summarized in the following table.

| I/O Type  | Description                                                            | No. of Pins |

|-----------|------------------------------------------------------------------------|-------------|

| Data I/O  | Datapath I/Os of FPGA fabric                                           | 29          |

| CLK       | Operating clock of FPGA core                                           | 1           |

| PROG_CLK  | Clock used by configuration protocol to program FPGA fabric            | 1           |

| CCFF_HEAD | Input of configuation protocol to load bitstream                       | 1           |

| CCFF_TAIL | Output of configuration protocol to read back bitstream                | 1           |

| TEST_EN   | Activate the test mode of FPGA fabric                                  | 1           |

| SC_HEAD   | Input of built-in scan-chain to load data to flip-flops of FPGA fabric | 1           |

| SC_TAIL   | Output of built-in scan-chain to read back flip-flops from FPGA fabric | 1           |

| IO_ISLO_N | Active-low signal to enable I/O datapath isolation from external ports | 1           |

| Total     |                                                                        | 37          |

Table 3.3: SOFA HD FPGA I/O usage and sizes

### 3.2.3 Accelerator Mode

When the Wishbone interface is enabled, the FPGA can operate as an accelerator for the RISC-V processor. Fig. 3.5 illustrates the detailed I/O arrangement for the FPGA, where the wishbone bus signals are connected to fixed FPGA I/O locations.

Note: Not all the 115 internal I/Os are used by the Wishbone interface. Especially, the I/O[21:29] are not connected.

**Warning:** The FPGA does not contain a Wishbone slave IP. Users have to implement a soft Wishbone slave when use the FPGA as an accelerator.

Fig. 3.5: I/O arrangement of *High-Density* (HD) FPGA IP when interfacing wishbone bus

### 3.2.4 Debug Mode

When the logic analyzer interface is enabled, the FPGA can operate in debug mode, whose internal signals can be readback through the registers of the RISC-V processor. Fig. 3.6 illustrates the detailed I/O arrangement for the FPGA, where the logic analyzer signals are connected to fixed FPGA I/O locations.

**Note:** The logic analyzer is 128-bit, while 115 bits can drive or be driven by the FPGA I/O. The other 14 bits are connected to internal spots of the FPGA fabric, monitoring critical signal activities of the FPGA in debugging purpose.

3.2. I/O Resources

Warning: If the logic analyzer is not used, please configure both the management SoC and the FPGA as follows:

- all the I/O directionality is set to input mode.

- all the output ports is pulled down to logic ``0``.

Fig. 3.6: I/O arrangement of *High-Density* (HD) FPGA IP when interfacing logic analyzer

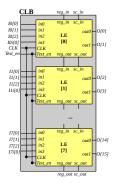

# 3.3 Configurable Logic Block

### 3.3.1 Generality

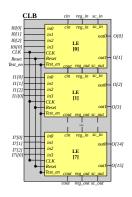

Each Logic Block (CLB) consists of 8 Logic Elements (LEs) as shown in Fig. 3.7. All the pins of the LEs are directly wired to CLB pins without a local routing architecture. Feedback connections between LEs are implemented by the global routing architecture outside the CLBs.

Fig. 3.7: Configurable logic block schematic

### 3.3.2 Multi-mode Logic Element

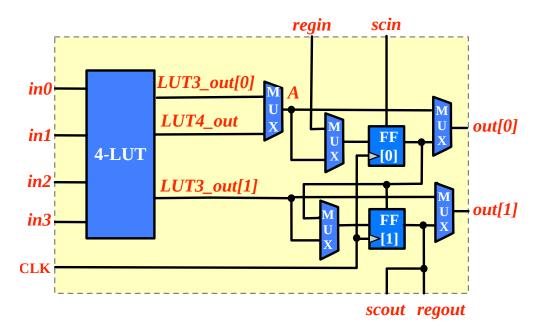

### **Physical Implementation**

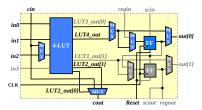

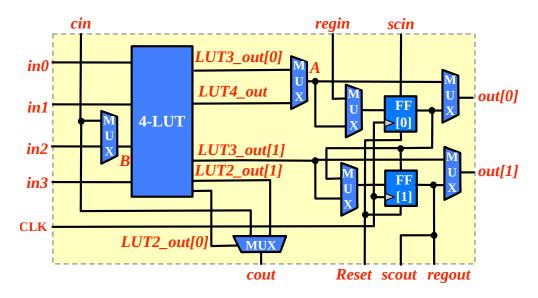

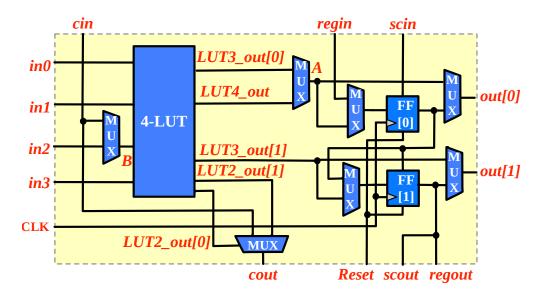

As shown in Fig. 3.8, each Logic Element (LE) consists of

- a fracturable 4-input Look-Up Table (LUT)

- two D-type Flip-Flops (FF)

The LE can operate in different modes to map logic function efficiently

• 4-input LUT and single FF (see details in *Operating mode:* LUT4 + FF).

Fig. 3.8: Detailed schematic of a logic element

- Dual 3-input LUTs and 2 FFs (see details in *Operating mode: Dual-LUT3*).

- 2-bit shift registers (see details in *Operating mode: Shift-Register*).

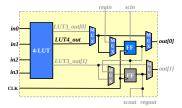

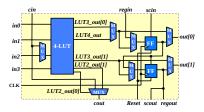

### Operating mode: LUT4 + FF

The logic element can operate in the Look-Up Table (LUT) + Flip-flop (FF) mode as many classical FPGA logic elements. As depicted in Fig. 3.9, the fracturable LUT will operate as a single-output 4-input LUT and the upper FF is used to implemented sequential logic.

The operating mode is designed to efficiently implement 4-input functions.

Fig. 3.9: Resource usage of the logic element operating in LUT4 + FF mode (Grey blocks and lines are unused resources).

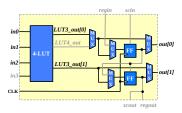

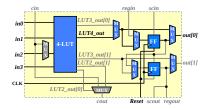

### **Operating mode: Dual-LUT3**

The logic element can operate in the dual Look-Up Tables (LUTs) and Flip-flops (FFs) mode as many modern FPGA logic elements. As depicted in Fig. 3.10, the fracturable LUT will operate as two 3-input LUTs with shared inputs.

The operating mode is designed to efficiently implement two 3-input functions with shared input variables. A popular example is the adder function, where the carry logic can be mapped to the upper LUT3 and the sum logic can be mapped to the lower LUT3.

Fig. 3.10: Resource usage of the logic element operating in dual LUT3 + FFs mode (Grey blocks and lines are unused resources).

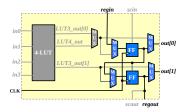

### **Operating mode: Shift-Register**

As depicted in Fig. 3.11, the Flip-flops (FFs) can be connected in dedicated routing wires to implement high-performance shift registers.

The operating mode is designed to efficiently implement shift registers which are widely used in buffer logic, e.g., FIFOs.

Fig. 3.11: Resource usage of the logic element operating in shift register mode (Grey blocks and lines are unused resources).

### 3.3.3 Scan Chain

There is a built-in scan-chain in the CLB where all the *sc\_in* and *sc\_out* ports of LEs are connected in a chain, as illustrated in Fig. 3.7. When *Test\_en* signal is active, users can readback the contents of all the D-type flip-flops of the LEs thanks to the scan-chain. When *Test\_en* signal is disabled, D-type flip-flops of the LEs operate in regular mode to propagate datapath signal from LUT outputs.

Note: The scan-chain of CLBs are connected in a chain at the top-level. See details in Scan-chain.

# 3.4 Circuit Designs

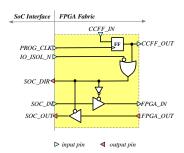

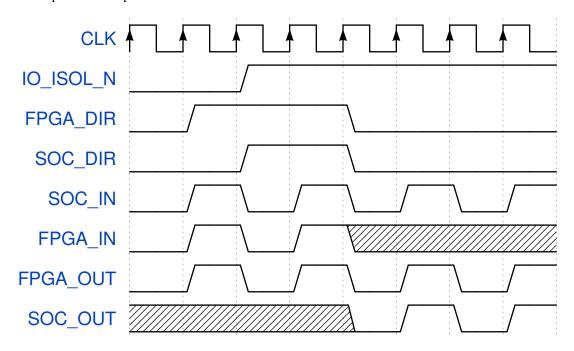

#### 3.4.1 I/O Circuit

As shown in Fig. 3.12, the I/O circuit used in the I/O tiles of the FPGA fabric (see Fig. 3.1) is an digital I/O cell with

• An active-low I/O isolation signal IO\_ISOL\_N to set the I/O in input mode. This is to avoid any unexpected output signals to damage circuits outside the FPGA due to configurable memories are not properly initialized.

**Warning:** This feature may not be needed if the configurable memory cell has a built-in set/reset functionality!

- An internal protection circuitry to ensure clean signals at all the SOC I/O ports. This is to avoid

- SOC\_OUT port outputs any random signal when the I/O is in input mode

- FPGA\_IN port is driven by any random signal when the I/O is output mode

- An internal configurable memory element to control the direction of I/O cell

The truth table of the I/O cell is consistent with the GPIO cell of Caravel SoC (which requires an active-low signal to enable output directionality), where

• When configuration bit (FF output) is logic 1, the I/O cell is in input mode

• When configuration bit (FF output) is logic 0, the I/O cell is in output mode

Fig. 3.12: Schematic of embedded I/O cell used in FPGA

Fig. 3.13 shows an example waveform about how the I/O cell works:

- When IO\_ISOL\_N is enabled/disabled

- When operates in input mode

- When operates in output mode

Fig. 3.13: An example of waveforms of embedded I/O cell used in FPGA

### 3.4.2 Multiplexer

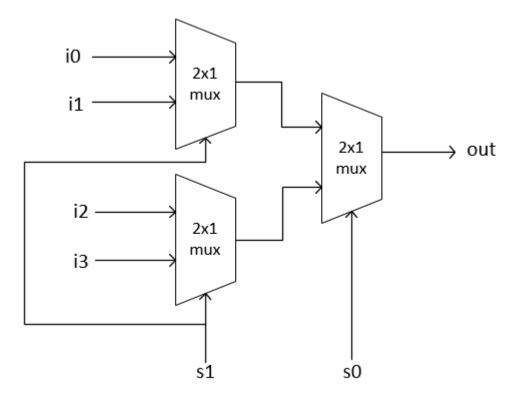

Routing multiplexer are designed by using the skywater *High-Density* (HD) 2-input MUX cell, as shown in Fig. 3.14. The tree-like multiplexer design is applied to all the routing multiplexers in logic elements, connection blocks and switch blocks across the FPGA fabric.

**Note:** Each routing multiplexer has a dedicated input which is connected to ground (GND) signal. When it is not used, the output will be driven by the ground, working as a constant generator.

3.4. Circuit Designs

Fig. 3.14: Schematic of multiplexer design in SOFA HD FPGA

# 3.5 Timing Annotation

## 3.5.1 Configurable Logic Block

The path delays in Fig. 3.15 are listed in Table 3.4.

Fig. 3.15: Schematic of a logic element used in SOFA HD FPGA

Table 3.4: Path delays of logic element in the SOFA HD FPGA

| Path / Delay          | TT (unit: ns) |

|-----------------------|---------------|

| in0 -> LUT3_out[0]    | 0.85          |

| in1 -> LUT3_out[0]    | 0.57          |

| in2 -> LUT3_out[0]    | 0.30          |

| in0 -> LUT3_out[1]    | 0.86          |

| in1 -> LUT3_out[1]    | 0.59          |

| in2 -> LUT3_out[1]    | 0.31          |

| in0 -> LUT4_out       | 1.14          |

| in1 -> LUT4_out       | 0.86          |

| in2 -> LUT4_out       | 0.58          |

| in3 -> LUT4_out       | 0.51          |

| LUT3_out[0] -> A      | 0.56          |

| LUT4_out[0] -> A      | 0.58          |

| A -> out[0]           | 0.88          |

| A -> FF[0]            | 0.56          |

| FF[0] -> out[0]       | 0.88          |

| LUT3_out[1] -> out[1] | 0.89          |

| LUT3_out[1] -> FF[1]  | 0.56          |

| FF[1] -> out[1]       | 0.89          |

| regin -> FF[0]        | 0.58          |

| FF[0] -> FF[1]        | 0.56          |

### 3.5.2 I/O Block

The path delays in Fig. 3.12 are listed in Table 3.5.

Table 3.5: Path delays of I/O circuit in the SOFA HD FPGA

| Path / Delay        | TT (unit: ns) |

|---------------------|---------------|

| SOC_IN -> FPGA_IN   | 0.11          |

| FPGA_OUT -> SOC_OUT | 0.11          |

# 3.5.3 Routing Architecture

The path delays in Fig. 3.2 are listed in Table 3.6.

Table 3.6: Path delays of routing blocks in the SOFA HD FPGA

| Path / Delay | TT (unit: ns) |

|--------------|---------------|

| A -> B       | 1.61          |

| A -> C       | 1.61          |

| A -> D       | 1.61          |

| B -> E       | 1.38          |

**CHAPTER**

**FOUR**

# **QLSOFA HD**

## 4.1 Architecture

# 4.1.1 Floorplan

QLSOFA HD FPGA share the same floorplan as SOFA HD FPGA. See details at *Floorplan*.

## 4.1.2 Tiles

The FPGA architecture follows a tile-based organization, to exploit the fine-grainularity in physical design, where three types of tiles are built:

Table 4.1: FPGA tile type and functionalities

| Type     | Capacity     | Description                                                                                                                                                                                                                            |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type CLB | Capacity 144 | Each CLB tile consists of - a Configurable Logic Block (CLB) - a X-direction Connection Block (CBx) - a Y-direction Connection Block (CBy) - a Switch Block (SB).  This is the majority tile across the fabric to implement logics and |

| IO-A     | 36           | registers.  The type-A I/O is a low-density I/O tile which is designed to mainly interface the GPIOs of the SoC.  Each I/O-A tile consists of 1 digitial I/O cell.                                                                     |

| ІО-В     | 12           | The type-B I/O is a high-density I/O tile which is designed to mainly interface the wishbone interface and logic analyzer of the SoC.  Each I/O-B tile consists of 9 digitial I/O cells.                                               |

# 4.1.3 Routing Architecture

The routing architecture shares the same principle as the SOFA HD routing architecture (See details in *Routing Architecture*).

**Note:** Different from SOFA HD, each routing channel consists of 60 routing tracks. See details in Table 4.2.

Table 4.2: Routing track distribution of QLSOFA HD FPGA

| Track type | Number of tracks per channel |

|------------|------------------------------|

| Length-1   | 6 (10%)                      |

| Length-2   | 6 (10%)                      |

| Length-4   | 48 (80%)                     |

| Total      | 60                           |

### 4.1.4 Scan-chain

QLSOFA HD FPGA share the same floroplan as SOFA HD FPGA. See details at Scan-chain.

### 4.2 I/O Resources

### 4.2.1 Pin Assignment

The QLSOFA HD FPGA IP has 144 data I/O pins as shown in Fig. 4.1.

Among the 144 I/Os,

- 29 external I/Os are accessible through the Caravel SoC's General-Purpose I/Os (GPIOs).

- 115 internal I/Os are accessible through the Caravel SOC's logic analyzer and wishbone interfaces, which are controlled by the RISC-V processor. See *Debug Mode* and *Accelerator Mode* for details.

**Warning:** For all the unused GPIOs, please set them to **input** mode, so that the FPGA will not output any noise signals to damage other SoC components.

**Note:** The connectivity of the 115 internal I/Os can be switched through a GPIO of Caravel SoC. As a result, the FPGA can operate in different modes.

**Warning:** The internal I/O pins will drive either Wishbone or the logic analyzer, following the same truth table as mode-switch bit in Fig. 4.1.

### 4.2.2 External I/Os

A QLSOFA HD FPGA IP contains 37 external I/O pins, including 27 data I/Os and 10 control I/Os.

Full details are summarized in the following table.

4.2. I/O Resources 23

Fig. 4.1: I/O arrangement of QLSOFA HD FPGA IP: switchable between logic analyzer and wishbone bus interface

I/O Type Description No. of Pins Data I/O Datapath I/Os of FPGA fabric 27 CLK Operating clock of FPGA core 1 PROG\_CLK Clock used by configuration protocol to program FPGA fabric 1 RESET Active-low reset for datapath flip-flops in the FPGA 1 PROG\_RESET 1 Active-low reset for configuration flip-flops in the FPGA CCFF HEAD Input of configuation protocol to load bitstream 1 CCFF TAIL Output of configuration protocol to read back bitstream 1 TEST\_EN Activate the test mode of FPGA fabric SC\_HEAD Input of built-in scan-chain to load data to flip-flops of FPGA fabric SC TAIL Output of built-in scan-chain to read back flip-flops from FPGA fabric IO\_ISLO\_N Active-low signal to enable I/O datapath isolation from external ports 1 Total 37

Table 4.3: SOFA HD FPGA I/O usage and sizes

### 4.2.3 Accelerator Mode

When the Wishbone interface is enabled, the FPGA can operate as an accelerator for the RISC-V processor. Fig. 4.2 illustrates the detailed I/O arrangement for the FPGA, where the wishbone bus signals are connected to fixed FPGA I/O locations.

Note: Not all the 115 internal I/Os are used by the Wishbone interface. Especially, the I/O[21:29] are not connected.

**Warning:** The FPGA does not contain a Wishbone slave IP. Users have to implement a soft Wishbone slave when use the FPGA as an accelerator.

Fig. 4.2: I/O arrangement of High-Density (HD) FPGA IP when interfacing wishbone bus

### 4.2.4 Debug Mode

When the logic analyzer interface is enabled, the FPGA can operate in debug mode, whose internal signals can be readback through the registers of the RISC-V processor. Fig. 4.3 illustrates the detailed I/O arrangement for the FPGA, where the logic analyzer signals are connected to fixed FPGA I/O locations.

**Note:** The logic analyzer is 128-bit, while 115 bits can drive or be driven by the FPGA I/O. The other 14 bits are connected to internal spots of the FPGA fabric, monitoring critical signal activities of the FPGA in debugging purpose.

Warning: If the logic analyzer is not used, please configure both the management SoC and the FPGA as follows:

- all the I/O directionality is set to **input mode**.

- all the output ports is pulled down to logic ``0``.

Fig. 4.3: I/O arrangement of *High-Density* (HD) FPGA IP when interfacing logic analyzer

# 4.3 Configurable Logic Block

### 4.3.1 Generality

Each Logic Block (CLB) consists of 8 Logic Elements (LEs) as shown in Fig. 4.4. All the pins of the LEs are directly wired to CLB pins without a local routing architecture. Feedback connections between LEs are implemented by the global routing architecture outside the CLBs.

Fig. 4.4: Configurable logic block schematic

### 4.3.2 Multi-mode Logic Element

### **Physical Implementation**

As shown in Fig. 4.5, each Logic Element (LE) consists of

- a fracturable 4-input Look-Up Table (LUT)

- two D-type Flip-Flops (FF)

Fig. 4.5: Detailed schematic of a logic element

The LE can operate in different modes to map logic function efficiently

- 4-input LUT and single FF (see details in *Operating mode:* LUT4 + FF).

- Dual 3-input LUTs and 2 FFs (see details in *Operating mode: Dual-LUT3*).

- 2-bit shift registers (see details in *Operating mode: Shift-Register*).

### Operating mode: LUT4 + FF

The logic element can operate in the Look-Up Table (LUT) + Flip-flop (FF) mode as many classical FPGA logic elements. As depicted in Fig. 4.6, the fracturable LUT will operate as a single-output 4-input LUT and the upper FF is used to implemented sequential logic.

The operating mode is designed to efficiently implement 4-input functions.

Fig. 4.6: Resource usage of the logic element operating in LUT4 + FF mode (Grey blocks and lines are unused resources).

### **Operating mode: Dual-LUT3**

The logic element can operate in the dual Look-Up Tables (LUTs) and Flip-flops (FFs) mode as many modern FPGA logic elements. As depicted in Fig. 4.7, the fracturable LUT will operate as two 3-input LUTs with shared inputs.

The operating mode is designed to efficiently implement two 3-input functions with shared input variables. A popular example is the adder function, where the carry logic can be mapped to the upper LUT3 and the sum logic can be mapped to the lower LUT3.

Fig. 4.7: Resource usage of the logic element operating in dual LUT3 + FFs mode (Grey blocks and lines are unused resources).

### Operating mode: Shift-Register

As depicted in Fig. 4.8, the Flip-flops (FFs) can be connected in dedicated routing wires to implement high-performance shift registers.

The operating mode is designed to efficiently implement shift registers which are widely used in buffer logic, e.g., FIFOs.

Fig. 4.8: Resource usage of the logic element operating in shift register mode (Grey blocks and lines are unused resources).

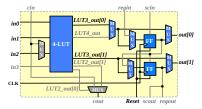

### Operating mode: Soft Adder

As depicted in Fig. 4.9, the 4-input LUT can implement an 1-bit adder logic, where carry inputs and outputs are connected through dedicated carry chain wires cin and cout across logic elements. This is more delay efficient than implementing adders through the dual LUT3 mode (see details in *Operating mode: Dual-LUT3*).

The operating mode is designed to efficiently implement multi-bit adders.

Fig. 4.9: Resource usage of the logic element operating in soft adder mode (Grey blocks and lines are unused resources).

#### 4.3.3 Scan Chain

There is a built-in scan-chain in the CLB where all the *sc\_in* and *sc\_out* ports of LEs are connected in a chain, as illustrated in Fig. 4.4. When *Test\_en* signal is active, users can readback the contents of all the D-type flip-flops of the LEs thanks to the scan-chain. When *Test\_en* signal is disabled, D-type flip-flops of the LEs operate in regular mode to propagate datapath signal from LUT outputs.

**Note:** The scan-chain of CLBs are connected in a chain at the top-level. See details in *Scan-chain*.

# 4.4 Circuit Designs

### 4.4.1 I/O Circuit

QLSOFA HD FPGA share the same I/O circuit design as SOFA HD FPGA. See details at I/O Circuit.

### 4.4.2 Multiplexer

QLSOFA HD FPGA share the same multiplexer design as SOFA HD FPGA. See details at *Multiplexer*.

# 4.5 Timing Annotation

### 4.5.1 Configurable Logic Block

The path delays in Fig. 4.10 are listed in Table 3.4.

Fig. 4.10: Schematic of a logic element used in QLSOFA HD FPGA

Table 4.4: Path delays of logic element in the QLSOFA HD FPGA

| Path / Delay          | TT (unit: ns) |

|-----------------------|---------------|

| in0 -> LUT3_out[0]    | 0.85          |

| in1 -> LUT3_out[0]    | 0.57          |

| in2 -> B              | 0.60          |

| B -> LUT3_out[0]      | 0.32          |

| in0 -> LUT3_out[1]    | 0.90          |

| in1 -> LUT3_out[1]    | 0.62          |

| B -> LUT3_out[1]      | 0.33          |

| in0 -> LUT4_out       | 1.17          |

| in1 -> LUT4_out       | 0.89          |

| in2 -> LUT4_out       | 1.21          |

| in3 -> LUT4_out       | 0.79          |

| LUT3_out[0] -> A      | 0.56          |

| LUT4_out[0] -> A      | 0.58          |

| A -> out[0]           | 0.88          |

| A -> FF[0]            | 0.56          |

| FF[0] -> out[0]       | 0.88          |

| LUT3_out[1] -> out[1] | 0.89          |

| LUT3_out[1] -> FF[1]  | 0.56          |

| FF[1] -> out[1]       | 0.89          |

| regin -> FF[0]        | 0.58          |

| FF[0] -> FF[1]        | 0.56          |

### 4.5.2 I/O Block

The path delays of I/O blocks in QLSOFA HD FPGA is same as the SOFA HD FPGA. See details in I/O Block.

# 4.5.3 Routing Architecture

The path delays in Fig. 3.2 are listed in Table 4.5.

Table 4.5: Path delays of routing blocks in the QLSOFA HD FPGA

| Path / Delay | TT (unit: ns) |

|--------------|---------------|

| A -> B       | 1.44          |

| A -> C       | 1.44          |

| A -> D       | 1.44          |

| B -> E       | 1.38          |

**CHAPTER**

**FIVE**

### **SOFA CHD**

### 5.1 Architecture

SOFA CHD FPGA share the same architecture as QLSOFA HD FPGA. See full details at *Architecture*.

### 5.2 I/O Resources

The SOFA CHD FPGA IP share the same I/O resource arragement as QLSOFA HD FPGA IP. See details at I/O Resources.

# 5.3 Configurable Logic Block

The SOFA CHD FPGA IP share the same *Configurable Logic Block* (CLB) architecture as QLSOFA HD FPGA IP. See details at *Configurable Logic Block*.

# 5.4 Circuit Designs

### **5.4.1 I/O Circuit**

SOFA CHD FPGA share the same I/O circuit design as SOFA HD FPGA. See details at I/O Circuit.

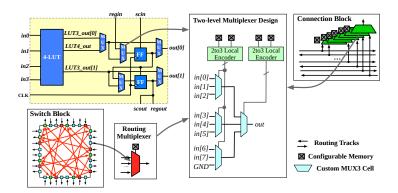

### 5.4.2 Multiplexer

Routing multiplexer are designed by using a few custom cells based on the Skywater *High-Density* (HD) PDK, as shown in Fig. 5.1. The multiplexer design follows a two-level structure, which is applied to all the routing multiplexers in logic elements, connection blocks and switch blocks across the FPGA fabric.

Each primitive in the two-level structure could be a 2/3/4-input custom cell, depending on the input size of the routing multiplexer. Each custom cell is built with input inverters and transmission-gates. For instance, Fig. 5.2 shows the transistor-level design of a 3-input custom cell.

**Note:** Each routing multiplexer has a dedicated input which is connected to ground (GND) signal. When it is not used, the output will be driven by the ground, working as a constant generator.

Fig. 5.1: Schematic of multiplexer design in SOFA CHD FPGA

Fig. 5.2: Detailed schematic of a 3-input custom cell in SOFA CHD FPGA

# **5.5 Timing Annotation**

# 5.5.1 Configurable Logic Block

The path delays in Fig. 5.3 are listed in Table 5.1.

Fig. 5.3: Schematic of a logic element used in SOFA CHD FPGA

Table 5.1: Path delays of logic element in the SOFA CHD FPGA

| Path / Delay          | TT (unit: ns) |

|-----------------------|---------------|

| in0 -> LUT3_out[0]    | 0.86          |

| in1 -> LUT3_out[0]    | 0.58          |

| in2 -> B              | 0.16          |

| B -> LUT3_out[0]      | 0.32          |

| in0 -> LUT3_out[1]    | 0.91          |

| in1 -> LUT3_out[1]    | 0.63          |

| B -> LUT3_out[1]      | 0.34          |

| in0 -> LUT4_out       | 1.20          |

| in1 -> LUT4_out       | 0.92          |

| in2 -> LUT4_out       | 0.78          |

| in3 -> LUT4_out       | 0.52          |

| LUT3_out[0] -> A      | 0.17          |

| LUT4_out[0] -> A      | 0.18          |

| A -> out[0]           | 0.48          |

| A -> FF[0]            | 0.15          |

| FF[0] -> out[0]       | 0.48          |

| LUT3_out[1] -> out[1] | 0.47          |

| LUT3_out[1] -> FF[1]  | 0.16          |

| FF[1] -> out[1]       | 0.37          |

| regin -> FF[0]        | 0.15          |

| FF[0] -> FF[1]        | 0.16          |

### 5.5.2 I/O Block

The path delays of I/O blocks in SOFA CHD FPGA is same as the SOFA HD FPGA. See details in I/O Block.

## 5.5.3 Routing Architecture

The path delays in Fig. 3.2 are listed in Table 5.2.

Table 5.2: Path delays of routing blocks in the SOFA CHD FPGA

| Path / Delay | TT (unit: ns) |

|--------------|---------------|

| A -> B       | 0.81          |

| A -> C       | 0.81          |

| A -> D       | 0.81          |

| B -> E       | 0.57          |

## 5.6 Custom Cells

## 5.6.1 Skywater Custom Multiplexer Cells

### **Background**

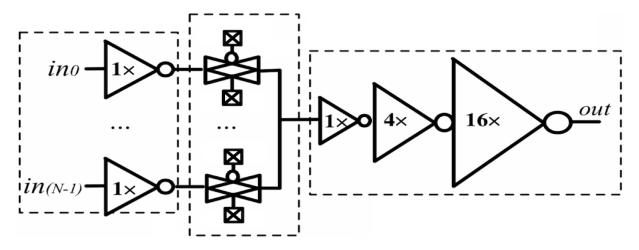

Traditionally, larger multiplexers are built using trees of smaller multiplexers as illustrated below:

Multiplexers trees lead to large power and timing constraints that limit FPGA performance. FPGA fabrics use complementary pass gate logic (CPL) to replace multiplexer trees with single level inverted transmission gate derived

multiplexers, as illustrated below:

Single level multiplexers are controlled through configuration SRAM cells which enable high impedance connections throughout the multiplexer hierarchy, thereby removing the need for hierarchical designs of multiplexers. Therefore, the CPL multiplexers enable increased performance and reduced power consumption throughout FPGA fabrics. Standard cells required for CPL multiplexers are not commonly included in PDKs, thereby requiring the need for custom cell creation to enable FPGA multiplexer hierarchies. The remainder of this document is dedicated to the architecture and performance evaluation of our <code>sky130\_uuopenfpga\_cc\_hd\_invmux2\_1/sky130\_uuopenfpga\_cc\_hd\_invmux3\_1</code> custom cells generated using the Skywater 130nm PDK. A comparison is achieved by generating 4-to-1 multiplexer and 6-to-1 multiplexers made from our cells and standard cells provided within the Skywater 130nm PDK.

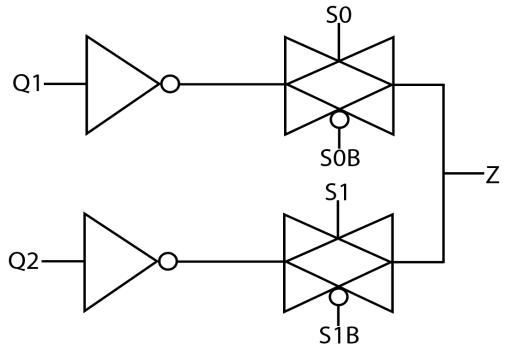

#### SKY130 UUOPENFPGA CC HD INVMUX2 1

- Usage: 2-Input Transmission Gate Multiplexer with Unity Drive Strength Inverter Input

- -Pins:

- Q1/Q2 Inverter Input

- S0/S1 NMOS Select Input

- S0B/S1B PMOS Select Input

- Schematic:

5.6. Custom Cells 35

schematic.png

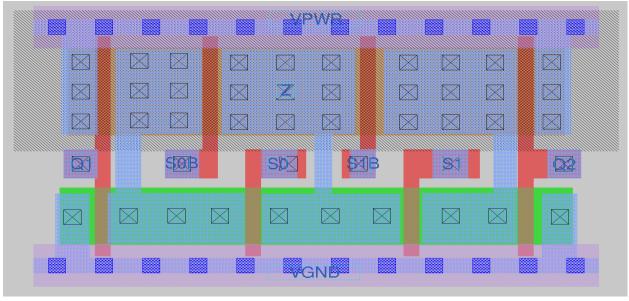

• Layout:

gds.png

• Comparison: To demonstrate the performance gains using CPL multiplexers, we built a 4-1 single level multiplexer using our custom <code>sky130\_uuopenfpga\_cc\_hd\_invmux2\_1</code> cell along with a 4-to-1 multiplexer using the <code>sky130\_fd\_sc\_hd\_mux2\_1</code> as the root cell of the multiplexer tree.

The *sky130\_fd\_sc\_hd\_mux2\_1* multiplexer is built using a static CMOS structure with a single select input, whereas our cell uses a fractured select hierarchy. To perform the comparisons we have tabulated values in regards to power, area, and timing for the 4-to-1 multiplexer tree using Cadence ADE XL.

#### • Power:

- sky130 uuopenfpga cc hd invmux2 1: 2.37 W

Our custom multiplexer provides a 22% reduction in power consumption.

- Area:

- sky130\_uuopenfpga\_cc\_hd\_invmux2\_1: 33.78 A<sup>2</sup>

- sky130\_fd\_sc\_hd\_\_mux2\_1: 33.78 A<sup>2</sup>

Our multiplexer implementation requires equal area neglecting interconnect overhead.

- Timing:

- sky130\_uuopenfpga\_cc\_hd\_invmux2\_1: 211.1 ps

- sky130\_fd\_sc\_hd\_\_mux2\_1: 304.3 ps

Our custom multiplexer provides over a 31% reduction in propagation delay.

SKY130\_UUOPENFPGA\_CC\_HD\_INVMUX2\_1 Cell Characterization

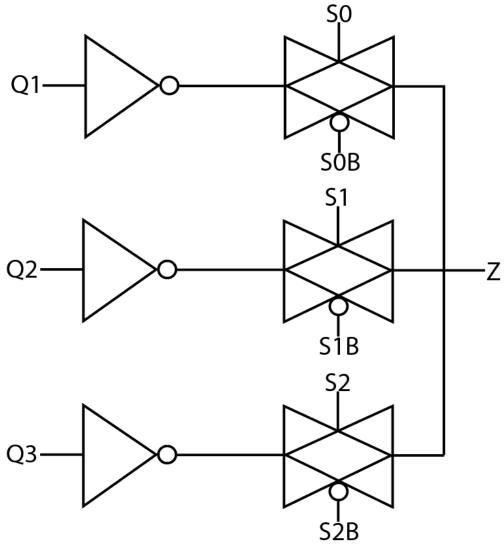

### SKY130\_UUOPENFPGA\_CC\_HD\_INVMUX3\_1

- Usage: 3-Input Transmission Gate Multiplexer with Unity Drive Strength Inverter Input

- Pins:

- \* Q2/Q3 Inverted Input

- \* S0/S1/S2 NMOS Select Input

- \* S0B/S1B/S2B PMOS Select Input

- Schematic:

5.6. Custom Cells 37

schematic.png

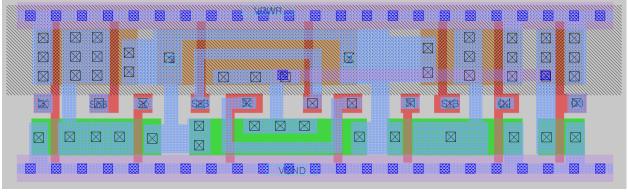

• Layout:

gds.png

• Comparison: To demonstrate the performance gains using CPL multiplexers, we built a 6-1 single level multiplexer using our custom <code>sky130\_uuopenfpga\_cc\_hd\_invmux3\_1</code> cell along with a 6-to-1 multiplexer using the <code>sky130\_fd\_sc\_hd\_mux4/2\_1</code> as the root cells of the multiplexer tree.

To perform the comparisons we have tabulated values in regards to power, area, and timing for the 4-to-1 multiplexer

tree using Cadence ADE XL.

#### • Power:

- sky130\_uuopenfpga\_cc\_hd\_invmux3\_1: 2.96 W

- sky130\_fd\_sc\_hd\_\_mux2\_1: 3.31 W

Our custom multiplexer provides a 10.5% reduction in power consumption.

#### • Area:

- sky130\_uuopenfpga\_cc\_hd\_invmux3\_1: 61.31 A<sup>2</sup>

- sky130\_fd\_sc\_hd\_\_mux2\_1: 48.80 A<sup>2</sup>

The Skywater multiplexer provides a 20% reduction in area.

#### • Timing:

- sky130\_uuopenfpga\_cc\_hd\_invmux3\_1: 272.6 ps

- sky130\_fd\_sc\_hd\_\_mux2\_1: 374.2 ps

Our custom multiplexer provides over a 27% reduction in propagation delay.

SKY130\_UUOPENFPGA\_CC\_HD\_INVMUX3\_1 Cell Characterization

5.6. Custom Cells 39

## **CHAPTER**

# SIX

# **CONTACTS**

### **General** Questions

Prof. Pierre-Emmanuel Gaillardon

pierre-emmanuel.gaillardon@utah.edu

Technical Questions about OpenFPGA

Prof. Xifan Tang

xifan.tang@utah.edu

Technical Questions about Physical Design

Ganesh Gore

ganesh.gore@utah.edu

**CHAPTER**

# **SEVEN**

# **ACKNOWLEDGMENT**

Supported by DARPA PoSH program

For more information on the OpenFPGA see openfpga\_doc or openfpga\_github For more information on the VPR architecture description language see xml\_vtr

For more information on the Skywater 130nm PDK see skywater\_pdk\_github

## **CHAPTER**

# **EIGHT**

# **INDICES AND TABLES**

- genindex

- modindex

- search

# **INDEX**

```

C

command line option

General, 41

Technical, 41

G

General

command line option, 41

T

Technical

command line option, 41

```